为万亿晶体管芯片铺路 英特尔展示有3个原子厚的2D新材料!

|

12月5日消息,在IEDM 2022(2022 IEEE国际电子器件会议)上,英特尔发布了多项突破性研究成果,继续探索技术创新,以在未来十年内持续推进摩尔定律,最终实现在单个封装中集成一万亿个晶体管。 英特尔的研究人员展示了以下研究成果:3D封装技术的新进展,可将密度再提升10倍;超越RibbonFET,用于2D晶体管微缩的新材料,包括仅三个原子厚的超薄材料;能效和存储的新可能,以实现更高性能的计算;量子计算的新进展。

英特尔技术开发事业部副总裁兼组件研究与设计总经理Gary Patton表示:“自人类发明晶体管75年来,推动摩尔定律的创新在不断满足世界指数级增长的计算需求。 在IEDM 2022,英特尔展示了其前瞻性思维和具体的研究进展,有助于突破当前和未来的瓶颈,满足无限的计算需求,并使摩尔定律在未来继续保持活力。” 此外,为纪念晶体管诞生75周年,英特尔执行副总裁兼技术开发总经理Ann Kelleher博士将于IEDM 2022主持一场全体会议。 届时,Kelleher将概述半导体行业持续创新的路径,即围绕系统级战略联合整个生态系统,以满足世界日益增长的计算需求并以更有效的方式实现创新,从而以摩尔定律的步伐不断前进。 此次会议将于太平洋标准时间12月5日周一上午9点45分(北京时间12月6日周二凌晨1点45分)开始,主题为“庆祝晶体管诞生75周年!摩尔定律创新的演进”。 对满足世界的无限计算需求而言,摩尔定律至关重要,因为数据量的激增和人工智能技术的发展让计算需求在以前所未有的速度增长。 持续创新正是摩尔定律的基石。在过去二十年,许多里程碑式的创新,如应变硅(strained silicon)、Hi-K金属栅极(Hi-K metal gate)和FinFET晶体管,都出自英特尔组件研究团队(Intel’s Components Research Group)。 这些创新在个人电脑、图形处理器和数据中心领域带来了功耗和成本的持续降低和性能的不断增长。 英特尔组件研究团队目前的路线图上包含多项进一步的研究,包括RibbonFET全环绕栅极(GAA)晶体管、PowerVia背面供电技术和EMIB、Foveros Direct等突破性的封装技术。

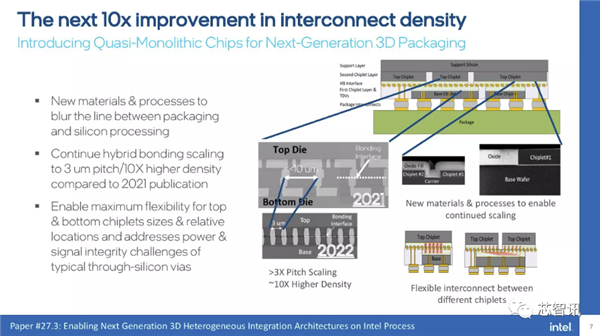

在IEDM 2022,英特尔的组件研究团队展示了其在三个关键领域的创新进展,以实现摩尔定律的延续:新的3D混合键合(hybrid bonding)封装技术,无缝集成芯粒;超薄2D材料,可在单个芯片上集成更多晶体管;能效和存储的新可能,以实现更高性能的计算。 英特尔组件研究团队所研发的新材料和工艺模糊了封装和芯片制造之间的界限。 英特尔展示了将摩尔定律推进到在单个封装中集成一万亿个晶体管的关键步骤,包括可将互联密度再提升10倍的先进封装技术,实现了准单片(quasi-monolithic)芯片。 英特尔还通过材料创新找到了可行的设计选择,使用厚度仅三个原子的新型材料,从而超越RibbonFET,推动晶体管尺寸的进一步缩小。 英特尔通过下一代3D封装技术实现准单片芯片: 与IEDM 2021上公布的成果相比,英特尔在IEDM 2022上展示的最新混合键合研究将功率密度和性能又提升了10倍。

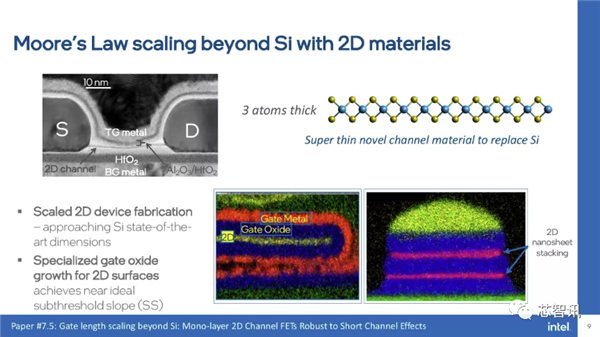

通过混合键合技术将互连间距继续微缩到3微米(去年还是10微米,现在缩小了超过3倍),英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽(相比去年论文提到的互联密度提升了10倍)。此外,混合键合技术还支持多个小芯片直堆叠。 英特尔探索通过超薄“2D”材料,在单个芯片上集成更多晶体管: 英特尔展示了一种全环绕栅极堆叠式纳米片结构,使用了厚度仅3个原子的2D通道材料,同时在室温下实现了近似理想的低漏电流双栅极结构晶体管开关。这是堆叠GAA晶体管和超越硅材料的固有限制所需的两项关键性突破。

目前的芯片材料,如硅,是由三维晶体组成,这意味着原子在所有三个维度上都键合在一起,因此对微缩提出了基本的限制。相比之下,2D材料很有吸引力,因为所有原子都粘在一个平面上。 目前的GAA设计由堆叠的水平硅纳米片组成,每个纳米片完全被一个门包围。 这种“环绕栅极”(GAA)技术可减少电压泄漏,从而防止关闭晶体管。随着晶体管的缩小,这正变得越来越成为一个问题——即栅极在三面环绕沟道时,正如我们在鳍式场效应晶体管中看到的那样。 英特尔将其 GAA 设计命名为 RibbonFET,计划于 2024 年上半年量产。然而,超越RibbonFET将需要进一步的创新,而这项2D材料研究符合潜在创新要求。 英特尔的论文描述了一种新的环绕栅极(GAA)堆叠纳米片结构,其通道材料(纳米片/纳米带)采用的是厚度仅为3个原子的2D材料,可以在室温下以低泄漏电流工作。

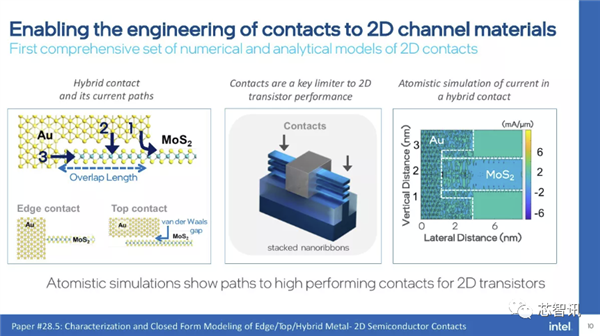

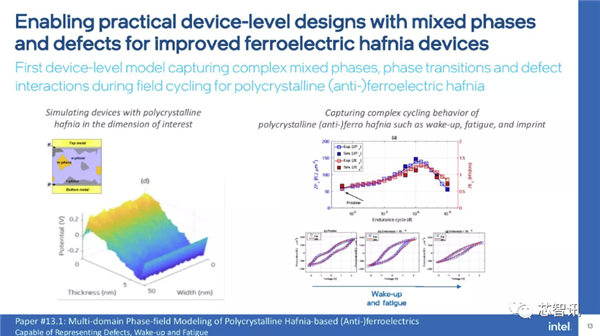

2D 通道材料的薄型使得建立与纳米带的电气连接成为一项艰巨的任务,因此英特尔的研究人员还展示了对2D材料的电接触拓扑结构(electrical contact topologies)的首次全面分析,为打造高性能、可扩展的晶体管通道进一步铺平道路。 为了实现更高性能的计算,英特尔带来了能效和存储的新可能: 通过开发可垂直放置在晶体管上方的存储器,英特尔重新定义了微缩技术,从而更有效地利用芯片面积。 英特尔在业内率先展示了性能可媲美传统铁电沟槽电容器(ferroelectric trench capacitors)的3D堆叠型铁电电容器(stacked ferroelectric capacitors),可用于在逻辑芯片上构建铁电存储器(FeRAM)。

这项技术最令人印象深刻的方面是,铁电沟槽电容器可以垂直堆叠在晶体管顶部的逻辑芯片上。 这使得存储器能够分层在逻辑元件之上,而不是像我们在其他类型的嵌入式存储器中看到的那样,如用于L1和L2缓存的SRAM,位于其自己的独特区域。 这种业界首创的器件级模型,可定位铁电氧化器件(ferroelectric hafnia devices)的混合相位和缺陷,标志着英特尔在支持行业工具以开发新型存储器和铁电晶体管方面取得了重大进展。 铁电存储器还具有与NAND闪存类似的功能,即在通常仅存储1bit的结构中存储多bit数据的能力。 在这种情况下,英特尔展示了每个沟槽存储4bit的能力。当然,这种方法将增加带宽和内存密度,同时减少延迟,产生更大、更快的片上缓存。

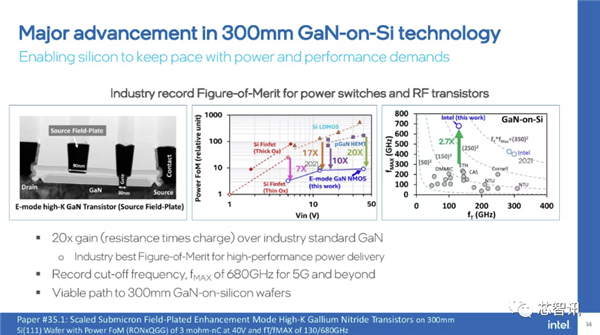

英特尔正在为打造300毫米硅基氮化镓晶圆(GaN-on-silicon wafers)开辟一条可行的路径,从而让世界离超越5G和电源能效问题的解决更进一步。英特尔在这一领域所取得的突破,实现了比行业标准高20倍的增益,并在高性能供电指标上打破了行业记录。

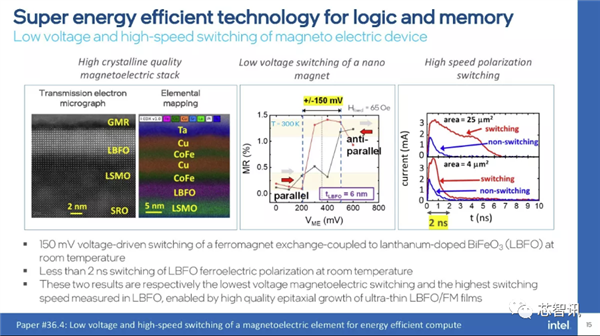

英特尔正在超高能效技术上取得突破,特别是在断电情况下也能保留数据的晶体管。对于三个阻碍该技术在室温下完全实现并投入使用的障碍,英特尔的研究人员已经解决其中两个。

英特尔继续引入新的物理学概念,制造用于量子计算的性能更强的量子位: 英特尔的研究人员加深了对各种界面缺陷(interface defects)的认识,这些缺陷可能会成为影响量子数据的环境干扰(environmental disturbances),从而找到了储存量子信息的更好方法。 Intel 18A提前到2024下半年量产 据英特尔最新对外公布的信息显示,Intel 4nm芯片已准备投产,它将用于包括Meteor Lake(14代酷睿流星湖)处理器、ASIC网络产品等。 同时,Intel 3nm、20A(2nm,其中A代表埃米,1nm=10埃米,下同)、18A(1.8nm)进展一切顺利,甚至还略有提前。 其中Intel 3nm将在明年下半年投产,用于Granite Rapids和Sierra Forest数据中心产品。

Intel 20A计划2024上半年准备投产,首发Arrow Lake(15代酷睿)客户端处理器,Intel 18A提前到2024下半年就绪,分别用在下一代酷睿和数据中心产品上。 |